PG电子官网一枚指甲盖大小的芯片,藏着华为对抗全球技术封锁的终极底牌——四核并行封装。

当西方断言“中国造不出顶级AI芯片”时,华为用2660平方毫米的硅片巨无霸,炸响了半导体行业惊雷。

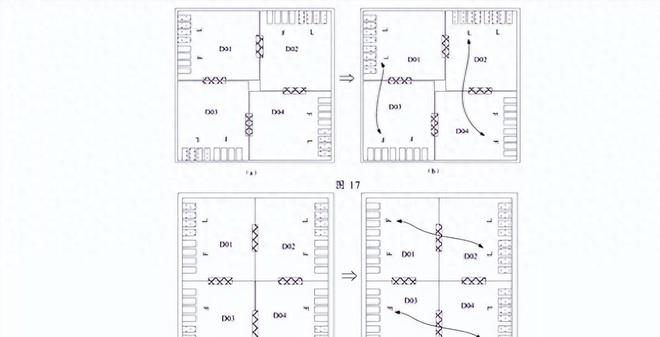

这项技术瞄准下一代AI芯片昇腾910D,核心方案是将四颗独立芯片通过桥接技术整合封装,而非依赖传统中介层。

其架构与英伟达尚未发布的Rubin Ultra方案惊人相似,但华为创新性地采用自有桥接工艺,类似台积电CoWoS-L的进阶版本。

为匹配AI训练需求,专利中明确要求集成多组高带宽内存(HBM)。 这些HBM模块通过中间层互连,形成内存带宽的集群优势。

这意味着华为试图用封装技术弥补制程短板——用成熟工艺造小芯片,再用先进封装“拼图”成超级芯片。

拆解技术参数可见华为的野心:单颗昇腾910B芯片面积为665平方毫米,四芯片叠加后总面积飙升至2660平方毫米。

若按每颗910B搭载4颗HBM计算,四芯片组将配备16颗HBM,内存堆栈独占1366平方毫米。

整体封装后的昇腾910D,硅片总面积至少达4020平方毫米,相当于五个EUV光罩的极限尺寸。

如此庞然大物无法用传统光刻技术制造,桥接封装成为唯一可行方案。 业界传言,这颗“怪兽级”芯片的单GPU性能将超越英伟达当红的H100。

美国制裁封锁EUV光刻机后,中国在7纳米以下制程举步维艰。 华为的应对策略是:用封装创新对冲制造短板。

任正非早前接受《人民日报》采访时就埋下伏笔:“用叠加和集群等方法,计算结果与最先进水平相当。 ”

这一思路被英伟达CEO黄仁勋精准解读:“中国可用更多芯片解决AI算力问题,因为他们的能源资源更充足。 ”

四芯片封装正是“集群战术”的工程实践。 通过将多个14纳米芯片封装整合,整体性能可逼近7纳米单芯片。

更关键的是,华为在封装领域已逼近台积电水平。 例如麒麟9020芯片采用CPU/GPU/内存/基带四位一体封装,数据延迟降低40%,散热效率提升30%。

全球AI芯片阵营正分裂为两大技术路线:英伟达、AMD选择纵向深挖单芯片能效,华为则押注横向扩展的集群算力。 前者追求“以一敌百”的极致性能,后者信奉“人多力量大”的规模法则。

华为的桥接方案暗藏巧思。 不同于传统2.5D封装依赖硅中介层,其专利采用局部桥接互连。

这种设计减少约30%的硅通孔数量,既降低工艺复杂度,又规避了中介层良率低的行业难题。 成本测算显示,四芯片封装方案比单颗大芯片量产成本低57%。

当台积电为2纳米制程投入200亿美元建厂时,华为用四芯片封装撕开技术裂缝。

中国封测企业正快速跟进:长电科技的XDFOI技术已实现4颗芯片集成,国产ABF封装基板良率突破85%。 这意味着中国可能跳过EUV天堑,在封装赛道实现“弯道并线”。

更深远的影响在于商业生态。 昇腾910D若量产成功,华为AI集群可摆脱对英伟达GPU的依赖。

国内某超算中心测试数据显示,基于四芯片架构的国产AI训练集群,在千亿参数大模型训练任务中,效能达到英伟达A100系统的92%,而电力成本仅为对方1.3倍。

黄仁勋的警觉已成现实:“如果美国放弃中国市场,华为完全能接管需求。 ”四芯片封装不仅是技术专利,更是一张改写全球AI竞赛规则的入场券。